Pesquisadores da École Polytechnique Fédérale de Lausanne (EPFL) e do Laboratório Hitachi Cambridge projetaram recentemente um circuito integrado (IC) que integra pontos quânticos de silício com eletrônica de leitura convencional. Este chip, apresentado em um artigo publicado na Nature Electronics, é baseado em uma tecnologia de semicondutor de óxido metálico complementar criogênico (CMOS) de 40 nm que está prontamente e comercialmente disponível.

“Nosso artigo recente se baseia na experiência dos dois grupos envolvidos”, disse Andrea Ruffino, uma das pesquisadoras da EPFL que realizou o estudo, ao TechXplore. “O objetivo do nosso grupo era construir circuitos integrados criogênicos (Bi)CMOS para leitura e controle de computadores quânticos, para serem co-empacotados ou co-integrados na fase final com processadores quânticos de silício. Por outro lado, a equipe da o Laboratório Hitachi Cambridge vem estudando dispositivos quânticos de silício há muitos anos.”

Ruffino e seus colegas da EPFL uniram forças com a equipe do Laboratório Hitachi Cambridge com o objetivo comum de unir circuitos clássicos e dispositivos quânticos em um único chip. Seu artigo baseia-se em alguns de seus esforços anteriores, incluindo a proposta de CMOS ICs criogênicos para computação quântica, bem como a realização de detecção rápida e multiplexada no tempo de dispositivos quânticos de silício.

“Em nosso novo artigo, tentamos propor uma versão de circuito totalmente integrado com o objetivo de demonstrar uma arquitetura escalável para leitura de dispositivos quânticos, a co-integração de eletrônicos clássicos e dispositivos quânticos em um único chip em uma tecnologia industrial, portão integrado leitura dispersiva baseada em frequências de micro-ondas e, finalmente, leitura multiplexada de tempo, frequência e tempo combinado/frequência”, explicou Ruffino.

O objetivo principal do estudo recente de Ruffino e seus colegas foi combinar as técnicas de detecção rápida e multiplexação de tempo desenvolvidas pela equipe do Hitachi Lab, para obter detecção multiplexada bidimensional (ou seja, tempo e frequência). Para conseguir isso, eles construíram uma matriz de transistores 2D e aplicaram essas duas técnicas a ela.

“Também queríamos integrar todos os componentes introduzidos em nossos trabalhos anteriores (ou seja, sensores, mecanismos e dispositivos de controle/acesso) em um único chip, usando tecnologia de fabricação padrão”, disse Tsung-Yeh Yang, pesquisador do Laboratório Hitachi Cambridge envolvido no estudo, disse ao TechXplore. “Portanto, o protótipo que demonstramos pode ser facilmente ampliado.”

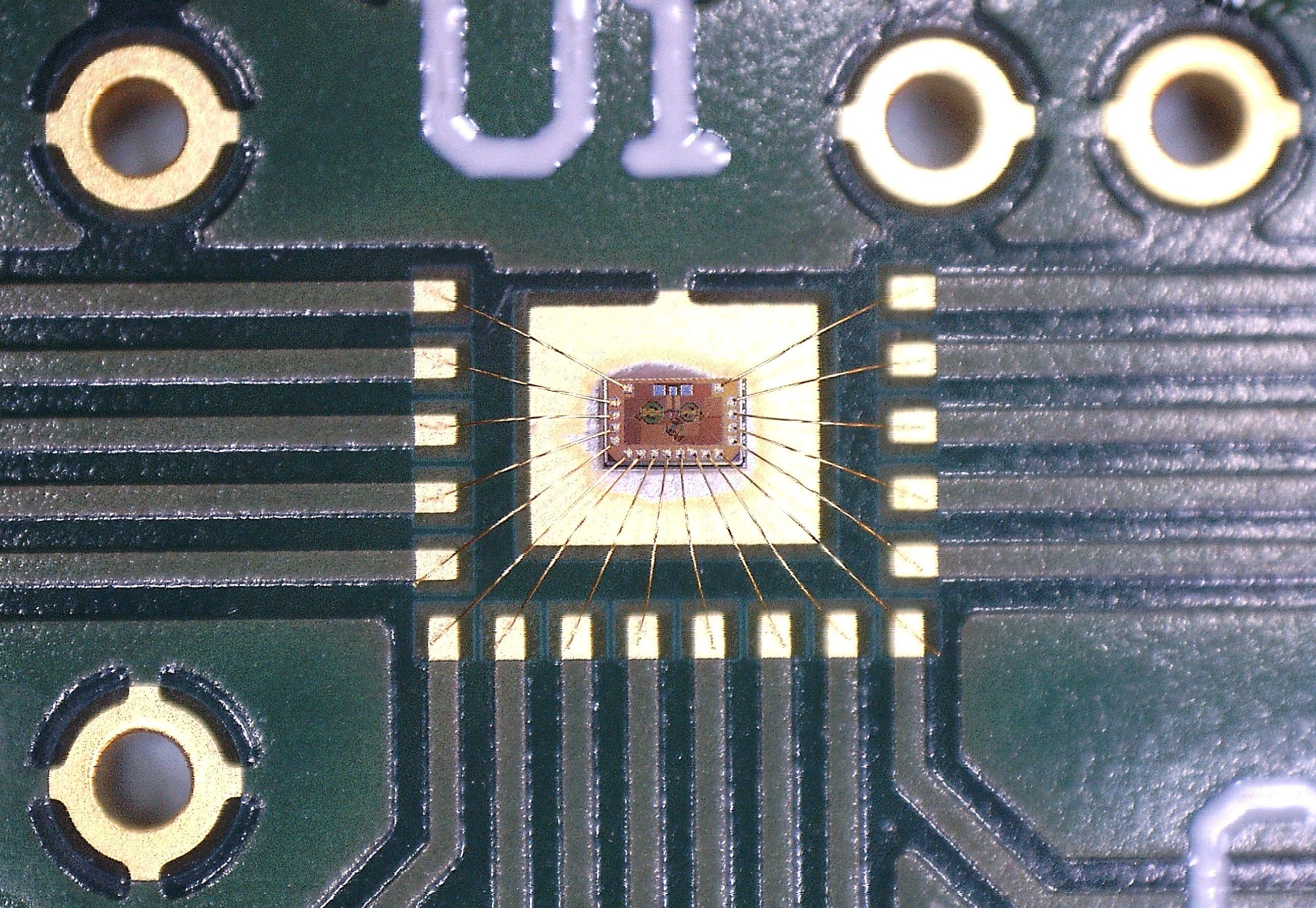

O chip projetado pelos pesquisadores é feito de transistores CMOS que se assemelham aos usados para fabricar smartphones e outros dispositivos eletrônicos comuns. Em contraste com os transistores convencionais, no entanto, os integrados dentro do novo chip operam em temperaturas criogênicas (ou seja, a 50 mK) e também contêm uma série de pontos quânticos de silício.

“Ao enviar um sinal de micro-ondas para o portão dos dispositivos quânticos e ler a resposta do sinal refletido, o estado dos dispositivos quânticos pode ser detectado”, explicou Ruffino. “Neste chip, a matriz de nove dispositivos quânticos é dividida em três linhas e três colunas. Cada linha é conectada a um ressonador de microondas que responde a uma frequência diferente, dando um recurso de multiplexação de frequência, e cada coluna é conectada para acessar transistores permitem conectar/desconectar os dispositivos quânticos, dando assim um recurso de multiplexação de tempo.”

O design exclusivo empregado por Ruffino e seus colegas permite que seu chip leia simultaneamente vários dispositivos quânticos conectados por um único fio e em diferentes frequências. Além disso, os dispositivos a serem lidos podem ser selecionados individualmente através dos transistores de acesso.

“O chip contém dois módulos principais: um módulo de dispositivo e um módulo de sensor”, disse Yang.

“O módulo do dispositivo é construído com uma matriz 2D de transistor de efeito de campo (MOSFET) semicondutor de óxido de silício metálico em massa de 40 nm, enquanto o módulo do sensor é construído com um ressonador de metal indutor-capacitor (LC) como o eletrômetro”.

Notavelmente, o chip dos pesquisadores integra todos os elementos necessários para ler informações, incluindo dispositivos quânticos, transistores clássicos e ressonadores de micro-ondas. Em contraste com outros chips desenvolvidos anteriormente, o IC pode ser usado para ler sistemas quânticos maiores, mantendo uma arquitetura flexível.

“A estrutura do nosso chip é baseada na arquitetura de memória dinâmica de acesso aleatório (DRAM), ou seja, uma estrutura de linha-coluna, para controlar/acessar a matriz MOSFET”, disse Yang.

“A primeira vantagem de usar a arquitetura DRAM é que o número de linhas de controle é dimensionado apenas sublinearmente com o número de FETs, em vez de dimensionar linearmente para o caso de uma linha-um-FET. A segunda é que os estados elétricos dos FETs são detectados por os ressonadores LC usando a técnica de reflectometria de frequência de microondas, que é mais rápida, com maior resolução e menos espaço no chip em comparação com a medição convencional de transporte dc.”

Uma das principais vantagens do novo chip é que seus dois módulos (ou seja, o dispositivo e os módulos de detecção) são combinados usando a tecnologia CMOS de 40nm padrão e disponível comercialmente. Isso significa que, no futuro, poderá ser facilmente fabricado em grande escala.

“Os MOSFETs de silício a granel de 40 nm que usamos se comportam como FETs típicos à temperatura ambiente”, disse Yang. “No entanto, descobrimos que os pontos quânticos (QDs), que são a base da construção de bits quânticos baseados em silício (qubits), podem ser induzidos em temperaturas criogênicas profundas (<-272 ° C) nos mesmos transistores. Nosso artigo também fornece uma demonstração do controle/acesso de uma matriz de transistores de ponto quântico bidimensional em uma arquitetura DRAM."

Usando seu IC, os pesquisadores foram capazes de demonstrar o sensor multiplexado de tempo e frequência 2D. Esses resultados demonstram que matrizes 2D de pontos quânticos baseados em silício podem ser fabricadas, controladas e monitoradas usando componentes eletrônicos existentes, como na tecnologia CMOS.

“Acho que as conquistas mais importantes deste trabalho são as demonstrações de que todos os elementos necessários para leitura (ou seja, dispositivos quânticos, transistores clássicos, ressonadores de microondas, etc.) podem ser integrados em um único circuito integrado em tecnologia comercial operando a 50 mK , que a leitura dispersiva de micro-ondas baseada em portas é possível em um único chip integrado e que a arquitetura proposta com multiplexação combinada de tempo e frequência permite ler um número maior de dispositivos quânticos, minimizando o número de fios necessários “, disse Ruffino.

No futuro, a arquitetura única introduzida por essa equipe de pesquisadores poderá ser usada para ler grandes matrizes 2D de pontos quânticos de silício, bem como qubits. Em última análise, isso poderia ajudar a resolver algumas das limitações relacionadas ao dimensionamento dos processadores quânticos de silício existentes.

Em seus próximos estudos, Ruffino, Yang e seus colegas planejam explorar a possibilidade de integrar qubits baseados em silício de alta fidelidade em sua arquitetura de chip proposta. Sua esperança é demonstrar controle/acesso e leitura de uma matriz qubit bidimensional usando uma arquitetura DRAM, que pode ser fabricada usando componentes eletrônicos existentes.

“Nossos planos para o desenvolvimento futuro nesta área estão principalmente na extensão deste trabalho para matrizes maiores e no aprimoramento de várias características de nossa demonstração, como a qualidade dos dispositivos quânticos e o fator de qualidade dos ressonadores de micro-ondas”, disse Ruffino. . “Além disso, nosso objetivo final de pesquisa será demonstrar nossa arquitetura em um sistema que implementa qubits de silício co-integrados”.

Publicado em 10/02/2022 12h19

Artigo original:

Estudo original: